硬件芯片篇 RISC-V處理器嵌入式開發(fā)者必看(上)

隨著開源指令集架構(gòu)RISC-V的興起,嵌入式開發(fā)領(lǐng)域迎來了新的機(jī)遇與挑戰(zhàn)。本文旨在為嵌入式開發(fā)者提供一份關(guān)于RISC-V處理器的入門指南,重點介紹其硬件芯片層面的關(guān)鍵特性與開發(fā)基礎(chǔ)。

一、RISC-V架構(gòu)的核心優(yōu)勢

RISC-V是一種基于精簡指令集計算(RISC)原則的開源指令集架構(gòu)(ISA)。其最大的特點在于開放、模塊化和可擴(kuò)展性。與傳統(tǒng)的專有架構(gòu)(如ARM、x86)相比,RISC-V允許開發(fā)者自由地設(shè)計、定制和優(yōu)化處理器,無需支付高昂的授權(quán)費用。這對于嵌入式系統(tǒng),尤其是成本敏感、需求多樣的物聯(lián)網(wǎng)(IoT)、邊緣計算和定制化硬件領(lǐng)域,具有革命性的意義。

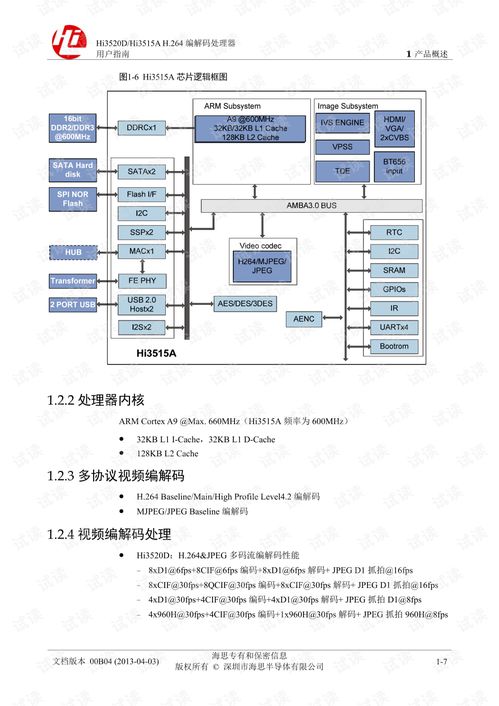

二、RISC-V處理器的硬件組成與特點

- 模塊化指令集:RISC-V ISA由基本整數(shù)指令集(I)和多個標(biāo)準(zhǔn)擴(kuò)展(如M-乘除法、A-原子操作、F/D-單/雙精度浮點、C-壓縮指令等)組成。開發(fā)者可以根據(jù)應(yīng)用需求,像搭積木一樣選擇必要的擴(kuò)展,實現(xiàn)功能與功耗、面積的精準(zhǔn)平衡。

- 精簡高效的設(shè)計:秉承RISC理念,RISC-V指令格式規(guī)整,解碼簡單,有利于提高流水線效率和主頻。其簡潔性也降低了設(shè)計驗證的復(fù)雜性,加速了芯片的研發(fā)周期。

- 活躍的硬件生態(tài):目前市場上已有多家廠商(如SiFive、嘉楠科技、平頭哥等)推出了商用的RISC-V內(nèi)核及SoC芯片,覆蓋從低功耗微控制器到高性能應(yīng)用處理器的廣闊范圍。開發(fā)者可以根據(jù)項目需求,選擇評估板或芯片進(jìn)行開發(fā)。

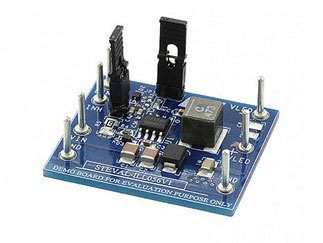

三、嵌入式開發(fā)者入門RISC-V的硬件準(zhǔn)備

- 開發(fā)板選擇:對于初學(xué)者或軟件開發(fā)者,選擇一款集成度高的RISC-V開發(fā)板是關(guān)鍵。例如,SiFive的HiFive系列、嘉楠科技的Kendryte K210開發(fā)板等都是不錯的起點。它們通常集成了處理器、內(nèi)存、外設(shè)和調(diào)試接口,方便快速上手。

- 工具鏈配置:RISC-V擁有成熟的開源工具鏈支持,包括GCC編譯器、GDB調(diào)試器、OpenOCD調(diào)試服務(wù)器等。需要根據(jù)目標(biāo)芯片的特定擴(kuò)展(如是否支持乘除法、壓縮指令等)來配置或獲取對應(yīng)的工具鏈。

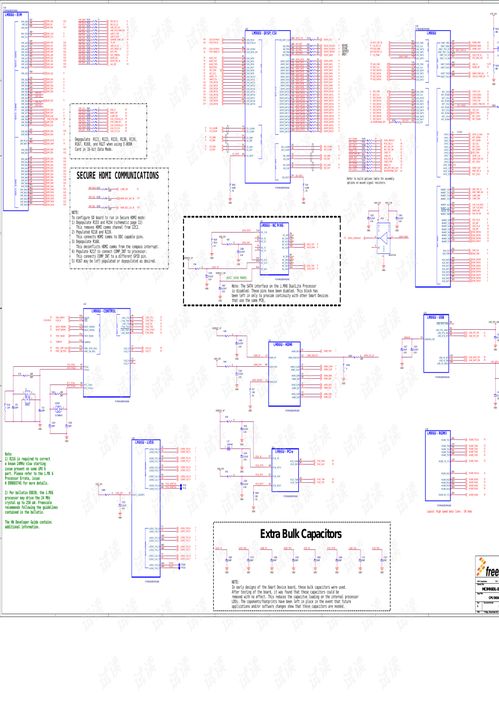

- 硬件調(diào)試接口:了解并熟悉JTAG或RISC-V標(biāo)準(zhǔn)的調(diào)試模塊(Debug Module)是進(jìn)行底層開發(fā)、固件調(diào)試的必備技能。這有助于開發(fā)者深入理解硬件行為,排查系統(tǒng)啟動、中斷處理等關(guān)鍵問題。

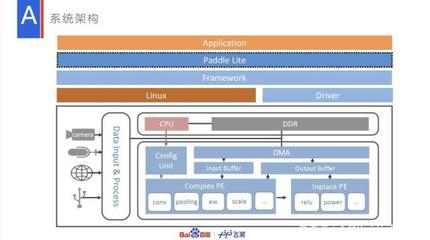

四、與軟件開發(fā)的銜接思考

雖然本文聚焦硬件芯片,但嵌入式開發(fā)始終是軟硬協(xié)同的藝術(shù)。RISC-V的硬件特性直接影響了軟件層的開發(fā):

- 指令集的選擇決定了編譯器優(yōu)化和匯編代碼的編寫。

- 內(nèi)存映射、中斷控制器、外設(shè)寄存器的配置是驅(qū)動開發(fā)和系統(tǒng)初始化的基礎(chǔ)。

- 開源硬件的可窺視性,使得開發(fā)者能更清晰地理解從代碼到電路執(zhí)行的整個鏈條,有助于編寫更高效的軟件。

在下一篇(下)中,我們將深入探討基于RISC-V的嵌入式軟件開發(fā)實踐,包括啟動流程、外設(shè)驅(qū)動、操作系統(tǒng)移植與優(yōu)化等內(nèi)容。對于嵌入式開發(fā)者而言,擁抱RISC-V不僅是學(xué)習(xí)一種新架構(gòu),更是參與到一場開源硬件變革中,開啟更靈活、創(chuàng)新的設(shè)計之門。

如若轉(zhuǎn)載,請注明出處:http://m.boxingw.cn/product/44.html

更新時間:2026-04-08 16:52:50